## Programming model for heterogeneous computing systems with customizable accelerators

Pervan, Branimir

**Doctoral thesis / Disertacija**

2022

Degree Grantor / Ustanova koja je dodijelila akademski / stručni stupanj: University of Zagreb, Faculty of Electrical Engineering and Computing / Sveučilište u Zagrebu, Fakultet elektrotehnike i računarstva

Permanent link / Trajna poveznica: https://urn.nsk.hr/urn:nbn:hr:168:513967

Rights / Prava: In copyright/Zaštićeno autorskim pravom.

Download date / Datum preuzimanja: 2025-01-09

Repository / Repozitorij:

FER Repository - University of Zagreb Faculty of Electrical Engineering and Computing repozitory

## FACULTY OF ELECTRICAL ENGINEERING AND COMPUTING

## Branimir Pervan

# PROGRAMMING MODEL FOR HETEROGENEOUS COMPUTING SYSTEMS WITH CUSTOMIZABLE ACCELERATORS

**DOCTORAL THESIS**

## FACULTY OF ELECTRICAL ENGINEERING AND COMPUTING

## Branimir Pervan

# PROGRAMMING MODEL FOR HETEROGENEOUS COMPUTING SYSTEMS WITH CUSTOMIZABLE ACCELERATORS

**DOCTORAL THESIS**

Supervisor: Associate Professor Josip Knezović, PhD

## FAKULTET ELEKTROTEHNIKE I RAČUNARSTVA

## Branimir Pervan

## PROGRAMSKI MODEL ZA RAZNORODNE RAČUNALNE SUSTAVE S PRILAGODLJIVIM UBRZIVAČIMA

**DOKTORSKI RAD**

Mentor: izv. prof. dr. sc. Josip Knezović

Zagreb, 2022.

| Doctoral thesis was made at the University of Zagreb, Faculty of Electrical Engineering and Computing, Department of Control and Computer Engineering |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| and companing, Department of Condor and Compater Engineering                                                                                          |

| Supervisor: Associate Professor Josip Knezović, PhD                                                                                                   |

| Doctoral thesis contains: 140 pages                                                                                                                   |

| Doctoral thesis number:                                                                                                                               |

## **About the Supervisor**

Josip Knezović, PhD is an associate professor at the Department of Control and Computer Engineering, Faculty of Electrical Engineering and Computing, University of Zagreb. He obtained his master's degree in 2005 and in 2009 he gained PhD degree with the thesis on the Streaming model of computation for image and video processing.

He is the member of the HPC Architecture and Application Research Center at FER. His research interests include energy efficient, embedded, heterogeneous and parallel computing systems and programming models, parallel programming, and computer architectures and applications of high-performance computing systems. He teaches several courses in undergraduate, graduate, and doctoral studies in computer science. From 2020 he serves as the Head of the Department of Control and Computer Engineering. He is a member of the IEEE, IEEE Computer Society, and ACM.

Personal page: https://www.fer.unizg.hr/rasip/jknezovic

## O mentoru

Izv. prof. dr. sc. Josip Knezović je izvanredni profesor u Zavodu za automatiku i računalno inženjerstvo Fakulteta elektrotehnike i računarstva Sveučilišta u Zagrebu. Stupanj magistra znanosti postigao je 2005. g., a 2009. g. obranio je doktorsku disertaciju na temu tokovnog računalnog modela za obradu slikovnih i video podataka.

Član je Centra za istraživanje arhitektura i aplikacija računarstva visokih performanci na FER-u. Njegovi istraživački interesi su energetski učinkoviti ugradbeni, heterogeni i paralelni računalni sustavi, paralelno programiranje i programski modeli, te računalne arhitekture i aplikacije u računarstvu visokih performanci. Nositelj je ili predavač na više predmeta na preddiplomskom, diplomskom i doktorskom studiju računarstva FER-a. Od 2020. g. obnaša dužnost predstojnika Zavoda za automatiku i računalno inženjerstvo. Član je strukovnih udruženja IEEE, IEEE Computer Society i ACM.

$O sobna\ stranica:\ http://www.fer.unizg.hr/rasip/jknezovic$

| Zahvaljujem prvo Bogu svemogućemu, onome koji bje, koji jest i koji će doći, iz kojega sve izvire i u kojega sve uvire.                                                                                                                                           |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Hvala mojoj supruzi Petri, kćeri Marti i sinu Boni. Vaša žrtva i odricanje protkani su ovim stranicama. Bez vaše pomoći ne bih uspio, moj uspjeh je i vaš uspjeh. Hvala i mojoj široj obitelji.                                                                   |

| Hvala mom mentoru Josipu za neizostavnu podršku koju mi je pružio tijekom rada na doktorskom studiju, te za sve trenutke u kojima smo se međusobno podučavali.                                                                                                    |

| Special thanks goes to Michel Steuwer at the University of Edinburgh and to his team from Edinburgh, Glasgow, and Münster. I cannot thank you enough for your help, support, and the ability to be a part of the team. Thank you for your expertise and patience. |

| Hvala svim mojim prijateljima, a ponajprije Barbari i Šili. Posebnu zahvalnost želim iskazati doktoru Turčinoviću, za svaki savjet, kavu, pelin, ručak, raspravu i druženje. Hvala i Emanuelu, Luki, Ivani, Igoru i Ani na podršci.                               |

|                                                                                                                                                                                                                                                                   |

| A ja, Bože sačuvaj da bih se ičim ponosio osim križem Gospodina našega Isusa Krista po    |

|-------------------------------------------------------------------------------------------|

| kojem je meni svijet raspet i ja svijetu.                                                 |

| (Gal 6, 14)                                                                               |

| I'd rather have questions that can't be answered than answers that can't be questioned.   |

| -R. Feynman                                                                               |

|                                                                                           |

| Those who would give up essential Liberty, to purchase a little temporary Safety, deserve |

| neither Liberty nor Safety.<br>-B. Franklin                                               |

|                                                                                           |

|                                                                                           |

|                                                                                           |

## **Abstract**

The constant growth of human development in general can be easily perceived at the current point in time. Followed by that development, there is a significant growth in the need for processing power. The amount of aggregated data requiring processing, followed by big data paradigm and brain-inspired computing drive the need to enter the so-called exascale domain, which is additionally confirmed by the existence of multiple scientific projects with the ultimate goal to develop an exascale machine in near future. In reaching the exascale domain, one of the key development points will be heterogeneity, implying systems containing a general-purpose processing core, coupled with at least one non-general purpose accelerator. Accelerators for specific applications usually achieve the best results regarding performance and energy efficiency, but with a cost of being unusable in other domains. Theoretically, there exists a large gap for customizable accelerators which could balance between performance and energy efficiency gains and the lack of customizability in conventional accelerators, by allowing customization of themselves to some extent.

High-performance systems of the future not only have to be heterogeneous but exploit parallelism on every level as well. However, efficiently exploiting heterogeneity and parallelism is inherently hard. Current programming models usually rely on imperative programming paradigms which decompose algorithms and problems with respect to *how* computations are executed, requiring deep knowledge of the underlying hardware and other aspects of the system, that domain scientists usually lack. It is, therefore, necessary to provide adequate models which would efficiently exploit given resources while keeping a relatively simple approach.

This thesis proposes a different approach to programming complex heterogeneous systems, by expressing *what* is being computed, rather than *how* computations are executed. To deliver such a model, the use of RISE language is proposed, which was appropriately extended to deliver the outcomes of this thesis. Additionally, ELEVATE, a domain-specific language for describing optimization strategies was used to demonstrate and enable optimizations targeting the specific parts of the system. As a testing platform, GAP8, a System-on-Chip containing a general-purpose fabric controller loosely coupled with a customizable accelerator containing eight RISC-V cores and a Hardware Convolution Engine was used. The proposed model was evaluated by executing typical parallel benchmarks and comparing the RISE-generated code with hand-tuned code. The results show that it is possible to provide an arguably simpler and more concise programming model while keeping performance and energy efficiency at least on par compared to the conventional programming model for the target platform.

**Keywords**: domain-specific languages, heterogeneous systems, parallel processing, multicore systems, RISC-V

## Prošireni sažetak

#### Programski model za heterogene računalne sustave s prilagodljivim ubrzivačima

#### 1. Uvod

Paralelno s rastom i razvojem znanosti te čovječanstva općenito, svakodnevno svjedočimo i povećanoj potrebi za računalnim resursima. Vršna performansa ponajboljih svjetskih superračunala trenutno je reda veličine 10<sup>15</sup>, dok se ulazak u *exaFLOPS* domenu anticipira za skoriju budućnost. Tomu svjedoče i projekti koji postoje na razini Europske Unije, u Japanu i SADu. Postizanje exaFLOPS domene otvara mnoga pitanja, primarno u područjima arhitekture računala, heterogenosti te energetske učinkovitosti. Pojedini izvori navode da je ključna točka razvoja za postizanje exaFLOPS domene upravo heterogenost. Heterogenost sustava obično implicira postojanje više od jedne vrste procesne jezgre na relativno izoliranom čvoru, a praktične implementacije svode se na uparivanje generičkog procesora (CPU) s grafičkim procesorom opće namjene (GPGPU) ili s ubrzivačem specifičnim za pojedinu aplikaciju. Grafički procesori opće namjene koriste se za intenzivne podatkovno paralelne zadatke dok, s druge strane, specijalizirani ubrzivači postižu maksimalnu performansu i energetsku učinkovitost, ali uz cijenu i iskoristivosti samo u jednoj aplikaciji, uz razvoj na razini dizajna hardvera. Uzevši u obzir prednosti i mane grafičkih procesora opće namjene te specijaliziranih ubrzivača, primjećuje se golem potencijal za uporabu prilagodljivih ubrzivača. Takvi ubrzivači kombinirali bi prednosti te minimizirali nedostatke oba pristupa tako da izlože parametre za prilagodbu čime bi se izbjegla zaključanost na samo jednu vrstu aplikacije, uz postizanje sumjerljive performanse i energetske učinkovitosti potpuno specijaliziranim ubrzivačima.

I dok je većina računala s kojima smo okruženi višejezgrena, promatrajući paralelizam i heterogenost u edukacijskim sustavima, većina obrazovnih programa podrazumijeva podučavanje sekvencijalnom programiranju. Na taj način stvara se procjep između teorije i prakse, s obzirom na to da se paralelno razmišljanje ne stvara ondje gdje bi se trebalo formirati. Jedan od razloga jest i inherentno teži način programiranja, te kompliciraniji programski modeli potrebni za razvoj paralelnih aplikacija.

Cilj ove disertacije, koji se nalazi na tromeđi heterogenosti, paralelizma, te prilagodbe programskih modela, jest izlaganje programskog modela visoke razine apstrakcije, oblikovanog kao domenski specifičan jezik za efikasno programiranje heterogenih sustava s prilagodljivim

ubrzivačima. Temeljna hipoteza istraživanja je ta da će programski kôd napisan u izloženom programskom modelu biti barem jednako performantan i jednako energetski efikasan kao i programski kôd napisan u nativnom modelu za ciljnu platformu, a sve uz povećan stupanj programirljivosti koji nudi programski model obrađen u disertaciji. Kao ciljna platforma koristit će se heterogeni sustav GAP8, koji se sastoji od generičkog procesora te prilagodljivog ubrzivača s osam jednostavnih jezgri te hardverskim ubrzivačem operacije konvolucije.

Konačno, izvorni znanstveni doprinos disertacije jest sljedeći:

- 1.Programski model za raznorodne sustave s prilagodljivim ubrziva čima temeljen na domenski specifičnom jeziku

- 2. Adaptivni mehanizam prilagodbe izraza za iskorištavanje sklopovskog ubrziva ča primjenom domenskih transformacija na višim razinama neovisnim o detaljima sklopovske platforme s ciljem optimizacije performanci i energetske učinkovitosti.

Prvi dio doprinosa ostvaren je kroz prilagodbu programskog jezika visoke razine apstrakcije RISE, dodavanje potrebnih primitiva te integraciju s ciljnom heterogenom platformom. Drugi dio doprinosa razvijen je dodatno umjesto razvoja algoritama za prilagodbu ubrzivača. Naime, prilagodljivi ubrzivači čije je skoro postojanje bilo anticipirano na javnom razgovoru nisu još dostupni u formi prototipa ili komercijalnog proizvoda, što je razvoj drugog dijela doprinosa ne samo učinilo izlišnim, nego ga i u potpunosti onemogućilo. Adaptivni mehanizam prilagodbe kao drugi dio doprinosa demonstrira mogućnosti apstrahiranja arhitekture sustava te ultimativno povećanje efikasnosti sustava te procesa programiranja.

## 2. Teorijska pozadina

Mooreov zakon koji se može tumačiti kao de facto standard za projekciju broja tranzistora na silikonu, prema riječima njegovog autora prestat će vrijediti u bližoj budućnosti. Nadalje, percipirani eksponencijalni rast efektivne računalne snage opada radi dostizanja tri fizikalne barijere ili zida, a to su zid snage, zid paralelizma na razini instrukcije, te zid memorije. Iz svega navedenoga izravno slijedi da hardver budućnosti mora biti višejezgren, a radi postizanja veće performanse, te da se programi za takav hardver moraju pisati tako da iskorištavaju dostupne mogućnosti. Temelj svake klasifikacije arhitektura računala jest Flynnova klasifikacija koja dijeli računala s obzirom na pristup tokovima instrukcija i podataka. Podjela paralelizma kao koncepta obično se temelji na podatkovnom paralelizmu koji se bavi načinom na koji se podaci distribuiraju računalnim čvorovima, dok s druge strane stoji paralelizam zadataka čiji je fokus na razdvajanju i raspoređivanju zadataka, također na različitim računalnim čvorovima.

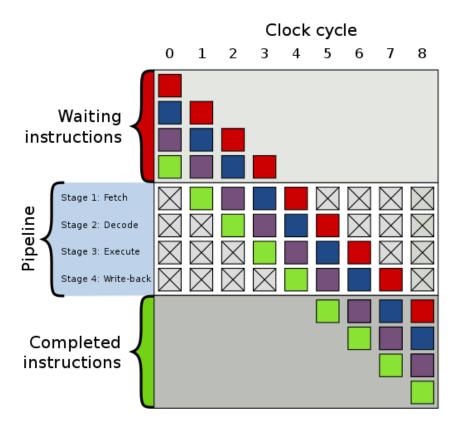

Iskorištavanje ovih dvaju navedenih tipova paralelizma moguće je na više razina. Paralelizam na razini instrukcije podrazumijeva preklapanje instrukcija tijekom njihovog izvođenja radi povećanja performansi. Tehnike za iskorištavanje ove vrste paralelizma su cjevovodi, odmotavanje petlji, predviđanje grananja te dinamičko raspoređivanje. Vektorske arhitekture predstavljaju drugi način iskorištavanja paralelizma, u kojem vektorski procesori kao prototipovi

SIMD arhitekture implementiraju ideju primjene jedne instrukcije paralelno nad više podataka. Paralelizam na razini dretve iskorištava se na razini operacijskog sustava, dok se paralelizam na razini zahtjeva obično iskorištava na visokim razinama gdje su zadaci koje računalo izvršava potpuno disjunktni. Programski modeli za paralelne sustave apstrahiraju paralelne arhitekture, a mogu se promatrati s obzirom na način na koji pristupaju dekompoziciji problema, te na način na koji procesi stupaju međusobno u interakciju. Dekompozicija problema svodi se na prethodno navedene podatkovni paralelizam i paralelizam zadataka, dok se modeli s obzirom na interakciju dijele na prosljeđivanje poruka, dijeljenu memoriju te implicitnu komunikaciju. Implementacije tih modela su obično Pthreads, OpenMP te MPI.

Heterogenost u kontekstu računalnih sustava implicira računalni sustav ili procesni čvor koji se sastoji od više jezgara različitih arhitektura. Implementacija takvih sustava najčešće znači korištenje procesora opće namjene uparenog s grafičkim procesorom opće namjene ili specijaliziranim ubrzivačem. Specijalizirani ubrzivači trenutno postižu najbolje performanse i energetsku učinkovitost, a trenutno se najčešće manifestiraju kao ubrzivači u domeni neuronskih mreža, kriptografskog procesiranja ili pojedinih matematičkih operacija. Prilagodljivi ubrzivači koji balansiraju između mogućnosti iskoristivosti u više domena, te performanse i energetske učinkovitosti trenutno su u razvoju. Također, ubrzivači te rekonfigurabilni hardver već je neko vrijeme dostupan u oblaku. Nasuprot ubrzivačima, grafički procesori opće namjene koriste se u podatkovno paralelnim aplikacijama te su već neko vrijeme razmjerno popularno rješenje u odgovarajućim problemskim domenama. Općenito, heterogenost se može postići i kombiniranjem različitih arhitektura konceptualno sličnih procesora.

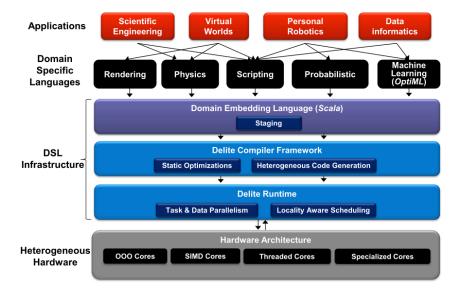

## 3. Općeniti koncepti

Programiranje i izvođenje aplikacija zaseban su problem u domeni heterogenog računarstva. Više različitih vrsta procesnih jedinica, kao i potencijalno dijametralno suprotne aplikacije koje bi se mogle izvoditi u sustavu predstavljaju značajan problem za programere. Jedan od mogućih rješenja jest podizanje razine apstrakcije razvojem programskog modela koji apstrahira arhitekturalne detalje sustava, često kao domenski specifičan jezik. Domenski specifični jezici su programski jezici koji korištenjem prikladnih oznaka i apstrakcija nude mogućnost izražavanja u jednoj problemskoj domeni. Interni domenski specifični jezici ugrađeni su unutar postojećeg programskog jezika, dok oni eksterni zahtijevaju razvoj vlastite prevoditeljske ili izvedbene infrastrukture. Jedan od programskih jezika opće namjene koji nude konstrukte kojima se olakšava razvoj domenskih specifičnih jezika jest Scala, a programsko rješenje koje se koristilo za razvoj doprinosa ove disertacije upravo je jezik duboko ugrađen u programskom jeziku Scala. Samo područje domenski specifičnih jezika trenutno uživa značajnu pozornost istraživačke i industrijske zajednice te se prirodno nameće kao rješenje za problem opisan disertacijom.

Kada se govori o heterogenom hardveru, ali i o otvorenom hardveru općenito, kao polazna osnova odabrana je arhitektura skupa instrukcija RISC-V. Arhitekture skupa instrukcija

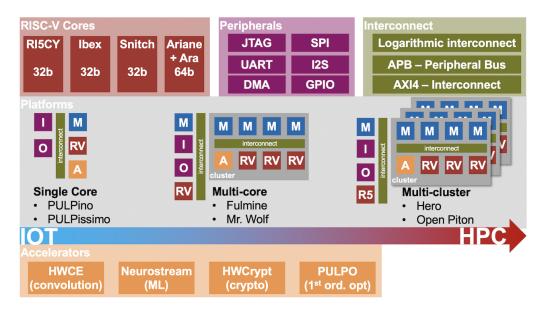

općenito apstrahiraju računalo na razini skupa asemblerskih instrukcija te predstavljaju sučelje između hardvera i softvera. RISC-V je jedan takav skup koji je trenutno uhvatio velik zamah u akademiji i industriji. Kako su argumentirali inicijalni autori koncepta, skup instrukcija procesora predstavlja najznačajnije sučelje u računalu općenito, te je logično da, s obzirom na to da ne postoji značajna tehnička zaprjeka, takvo sučelje bude otvoreno. Sam RISC-V procesor je zamišljen da bude jednostavan, ali da anticipira različite primjene, od ugradbenih računala, do poslužitelja. Iz perspektive arhitekture, procesor je vrste *load-store* s *little-endian* poretkom bajtova te operacijama kojima su operandi registri. RISC-V arhitektura je također modularna i tipično se sastoji od baznog i minimalnog skupa instrukcija te proširenjima koje odgovaraju potrebama računala koje se dizajnira. Bazni instrukcijski skupi podržavaju cjelobrojne skupove ili ugradbene skupove sa širinama adresa od 32, 64 ili 128 bita. Ekstenzije instrukcijskom skupu dodaju različite funkcionalnosti, od hardverskog množila, podrške za floating-point operacije različitih preciznosti, kompresirane instrukcije, vektorske operacije i sl. Za validnost službenog dijela instrukcijskog skupa brine se neprofitna udruga, a korisnici mogu samostalno proširivati instrukcijski skup korištenjem ekstenzije X. Heterogeni sustav GAP8 korišten kao hardverska platforma u ovoj disertaciji koristi procesorske jezgre RISC-V tipa RV32IMC.

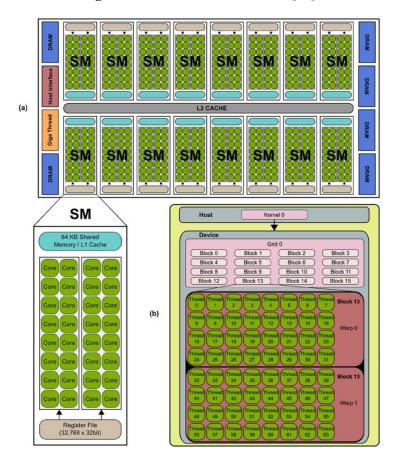

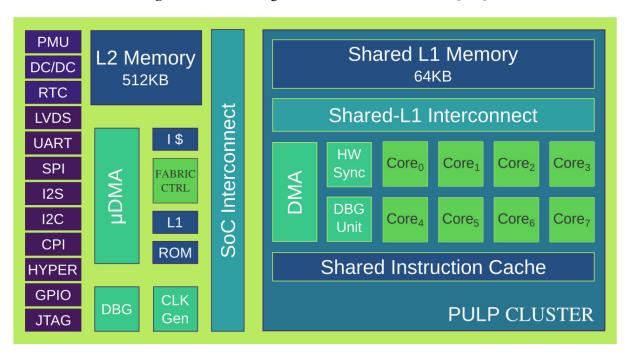

Jedan od većih projekata proizašao iz RISC-V ekosustava jest PULP. PULP je krovni projekt dvaju europskih sveučilišta čiji je cilj razvoj otvorenih i slobodnih hardverskih platformi za potrebe istraživanja i industrije. Projekt za cilj ima optimiranje potrošnje energije na skali milivata kako bi zadovoljio računalne potrebe aplikacija u internetu stvari. Hardver koji proizlazi iz projekta je relativno modularan što omogućava razvoj i optimiranje hardvera za specifične aplikacije uz postizanje značajnih stupnjeva optimizacije i energetske učinkovitosti. Projekt obuhvaća procesore, jednojezgrene sustave, višejezgrene sustave, višeklasterske sustave, te akceleratore. Iz projekta je proizašla i platforma GAP8, korištena kao ciljni hardver u disertaciji. Konkretno, korišten je koncept višejezgrenog sustava (projekt *Mia Wallace*), višeklasterskog sustava (projekt *HERO*) te ubrzivač (projekt *HWCE*).

GAP8 je heterogena računalna platforma proizvođača GreenWaves Technologies, a primaran joj je cilj pružiti mogućnost relativno visokih performansi na rubnim uređajima koji radi svojih specifičnih zahtjeva, npr. baterijskog napajanja, moraju ostati u domeni niske potrošnje. GAP8 primarno se sastoji od dva disjunktna dijela, od *fabric* kontrolera koji gravitira oko procesora opće namjene, te oko prilagodljivog ubrzivača. *Fabric* kontroleru sadrži procesor opće namjene arhitekture RV32IMC, a primarna zadaća mu je pokretanje sustava, aplikacija te orkestriranje vanjskih jedinica. S druge strane, klaster se sastoji od osam RISC-V jezgri identične arhitekture kao i procesor opće namjene u *fabric* kontroleru, te dodatno sadrži i specijalizirani hardverski ubrzivač operacije konvolucije. Memorijski podsustav GAP8 ugrubo se može podijeliti na memoriju dostupnu isključivo *fabric* kontroleru, memoriju dostupnu isključivo jezgrama u klasteru, podijeljenu po segmentima za svaku procesorsku jezgru, te memoriju kojoj

mogu pristupiti oba podsustava. Upravo je potonja korištena za izvedbu doprinosa disertacije. Iako najsporija, ta je memorija najveća te za prednost ima mogućnost pristupa iz oba podsustava čime se omogućava jednostavan pristup bez sinkronizacijskih mehanizama. Hardverski ubrzivač operacije konvolucije sklopovski izvodi operaciju konvolucije nad dvodimenzionalnim ulaznim signalom, te filtrima dimenzija  $3 \times 3$ ,  $5 \times 5$ ,  $7 \times 7$  te  $7 \times 4$ . Ubrzivač je izložen kroz zaseban API koji se pokazao relativno nestabilnim, pogotovo u kontekstu disjunktnog korištenja u odnosu na komponente SDK-a namijenjene procesiranju inferencije na neuronskim mrežama u klasteru.

#### 4. Programski okvir RISE

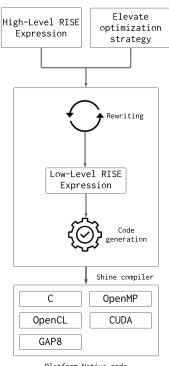

RISE je podatkovno paralelan programski jezik temeljen na uzorcima, visoke razine apstrakcije te izveden kao domenski specifičan jezik, duboko ugrađen unutar programskog jezika Scala. Glavni naglasak programskog jezika RISE jest izlaganje sučelja koje će omogućiti programerima te znanstvenicima unutar specifičnih domena da izračune opišu odgovarajući na pitanje što treba izračunati, umjesto da nizom imperativnih naredbi opisuju kako se pojedina operacija treba izvesti. RISE je uparen s programskim jezikom ELEVATE, također izvedenim u obliku domenski specifičnog jezika unutar programskog jezika Scala, a čija je glavna uloga izražavanje optimizacijskih strategija. Oba jezika ulaz su u prevoditelj Shine koji primjenjuje transformacije te generira optimirani kôd niske razine. Cjeloviti RISE okvir razvija se na Sveučilištima u Edinburghu, Glasgowu i Münsteru, te je korišten za ostvarivanje doprinosa ove disertacije. Ulaz u prevoditelj jest izračun izražen u programskom jeziku RISE, te optimizacijska strategija u programskom jeziku ELEVATE. Prevoditelj u procesu prepisivanja primjenjuje transformacije te generira RISE izraz niske razine u kojemu su direktno enkodirane optimizacijske odluke. Nadalje, u procesu prepisivanja koristi se hibridni funkcijskoimperativan međureprezentacijski jezik DPIA (Data Parallel Idealised Algol). RISE izraz niske razine prepisuje se u funkcijsku DPIA međureprezentaciju, a nakon toga u imperativnu DPIA međureprezentaciju. Ta se imperativna međureprezentacija na kraju prevodi u čvorove apstraktnog sintaksnog stabla za ciljni programski jezik ili platformu, te u konačnici u sam programski kôd niske razine, nativan za ciljnu platformu.

Programski jezik RISE sadrži standardne konstrukte tipične za (funkcijske) programske jezike općenito, primjerice identifikatore, lambda izraze ili literale. Posebna vrsta izraza su primitivi koji enkapsuliraju modularne operacije više ili niže razine. Primitivi mogu biti generički, odnosno primjenjivi na sve ciljne platforme, ili mogu biti specijalizirani za pojedinu platformu. Generički primitivi obuhvaćaju funkcije koje se mogu pronaći u drugim (funkcijskim) programskim jezicima, uključivo funkcije višeg reda, primjerice *map* i *reduce*, ali i *zip*, *join*, *slide* ili *pad*. S druge strane, optimizacijske strategije u programskom jeziku ELEVATE izražavaju se pravilima koja se onda ulančavaju odgovarajućim operatorima. Pravila prepisivanja mogu biti algoritamska, pa na taj način matematički dokazivim pravilima optimirati

izračun kombinacijom primitiva, npr. pravilo *mapFusion*. Također, pravila mogu biti i jednostavnija (*eng. lowering*) te se mogu koristiti za zamjenu generičkih primitiva konkretnim implementacijama. Jednostavan primjer jest zamjena generičkog primitiva *map* konkretnom paralelnom implementacijom *mapPar*. Pravila se primjenjuju ondje gdje je određeno kombinatorima koji rekurzivnim prolaskom kroz izraz u programskom jeziku RISE traže odgovarajuće uzorke te ih prepisuju kako pravilo nalaže. Konkretni kombinatori mogu tražiti uzorke izvana, iznutra ili unutar cijelog izraza.

## 5. Implementacija modela

Prvi dio očekivanog znanstvenog doprinosa ostvaren je korištenjem i odgovarajućim proširenjima programskog jezika RISE, te pripadajućeg radnog okvira. S obzirom na to da ciljna heterogena platforma GAP8 dijeli neke koncepte s platformama podržanima od strane jezika OpenCL, a primarno koncept domaćina (eng. host) i uređaja (eng. device) u sustavu koji idejno odgovaraju fabric kontroleru i klasteru na platformi GAP8, implementacija se u većim dijelovima oslanja upravo na komponente inicijalno predviđene za platformu OpenCL. Doprinos je u većoj mjeri ostvaren kroz komponente modula, generatora modula te generatora kôda. Prva razvijena komponenta je GAP8 Module koja enkapsulira validan dio kôda koji se može pokrenuti na ciljnoj platformi, na način da sadržava podmodul za domaćina te sekvencu podmodula za uređaj tj. klaster. Jedna aplikacija enkapsulirana na ovaj način može podržavati više funkcija koje će se izvršiti na klasteru. Oba podmodula su vrste modula za programski jezik C. Modul dodatno sadržava metodu koja ga prevodi u ciljni programski jezik te je zadužen za injektiranje odsječka kôda za raspakiravanje parametara unutar funkcije koja se izvodi na klasteru. S obzirom na to da API za GAP8 ne podržava slanje više od jednog parametra u trenutku pokretanja izvođenja na klasteru, injektiraju se odsječci kôda koji u strukturu pakiraju parametre prije slanja, castaju strukturu u pokazivač tipa void, te nakon zaprimanja takvog parametra na strani klastera, ponovno ga otpakiravaju u zasebne parametre. Modul je zadužen za otpakiravanje parametara dok se pakiranje parametara događa prilikom generiranja kôda za stranu domaćina.

Odgovornost generiranja kôda podijeljena je među komponentama zaduženima za stranu akceleratora, tj. klastera, te domaćina. Dodatno, strana domaćina sadržava i generator modula za domaćina. Strana klastera ponovno iskorištava ranije ugrađene mogućnosti radnog okvira te se na njih oslanja prilikom generiranja modula za klaster. Generiranje kôda za klaster izvedeno je proširenjem postojećeg generatora za model OpenMP te se na ovoj razini dodaje podrška za hardverski ubrzivač operacije konvolucije. U slučaju nailaska na odgovarajući imperativni DPIA primitiv, generator kôda generirat će seriju poziva koji na niskoj razini omogućuju izvedbu operacije konvolucije na hardverskom ubrzivaču. Ti koraci su: instanciranje i pokretanje ubrzivača operacije konvolucije, odgovarajuća konfiguracija, izvršavanje operacije te u konačnici isključivanje ubrzivača. S druge strane, s obzirom na to da paralelizam nije izvediv na strani domaćina, generator kôda za procesor domaćina oslanja se na generator za programski

jezik C. Primarna zadaća ovog generatora jest generiranje poziva za niske razine za izvršavanje izračuna na klasteru, pakiranje parametara koji se prosljeđuju klasteru te generiranje memorijskih sinkronizacijskih poziva. Iako se trenutno sinkronizacija memorije ne provodi nego se aplikacije oslanjaju na mogućnost izravnog pristupa podacima koji se nalaze u memoriji dostupnoj s obje strane sustava, preuzimanjem koncepta iz podrške za OpenCL platforme prevoditelj anticipira buduću mogućnost za takvom sinkronizacijom. Na taj način stvara se preduvjet za buduće optimiranje generiranog kôda s obzirom na prijenos podataka s domaćina na klaster i obrnuto. Generator modula domaćinskog kôda ulančava tok koji zadaje sučelje generatora modula na način da ponovno iskorištava dijelove generatora za platformu OpenCL te ih povezuje s direktivama za generiranje kôda i generiranje modula domaćinskog kôda. Produkt generatora modula domaćinskog kôda jest modul za programski jezik C koji enkapsulira strukturu s varijablom tipa *Kernel* za svaku funkciju koja se izvodi na klasteru, *typedef* deklaraciju za navedenu strukturu, direktivu uključivanja za odgovarajuću *header* datoteku s podrškom za izvedbenu okolinu, seriju funkcija za inicijaliziranje, pokretanje i uništavanje *kernela*, te u konačnici funkciju *main* kao ulaznu točku za izvršavanje aplikacije.

Ključna funkcionalnost sustava jest mehanizam za pokretanje izvođenja na klasteru, a ona je ostvarena kroz dodavanje odgovarajućih primitiva na svim razinama jezika, odnosno radnog okvira. Na razini programskog jezika RISE, dodan je primitiv gap8run koji kao parametar prima broj jezgri na kojem se izračun želi izvršiti, dok kao drugi parametar prima izraz u programskom jeziku RISE kojim je opisan izračun. Na razini funkcijske DPIA međureprezentacije, dodana su dva primitiva, Run te KernelCall. Primitiv Run je primitiv u koji se gap8run inicijalno prevodi, a koji se u procesu odvajanja razdvajanja inicijalnog izraza na dio koji će se izvršiti na domaćinu te na dio koji će se izvršiti na klasteru prevodi u primitiv KernelCall. Razdvajanje izraza na ta dva dijela odvija se u komponenti SeparateHostAndAcceleratorCode a svodi se na obilaženje izraza te konstrukciju funkcijske definicije kada se naiđe na dio izraza koji je za izvođenje na klasteru označen prethodno navedenim gap8run primitivom. Naposljetku, funkcijski DPIA primitiv KernelCall prevodi se u imperativni DPIA primitiv KernelCallCmd koji direktno uzrokuje generiranje konstrukata za pokretanje zadanog izraza u klasteru. Za podršku hardverskog ubrzivača operacije konvolucije dodana su po četiri primitiva na svakoj razini, tj. na razini programskog jezika RISE te na razinama imperativne odnosno funkcijske DPIA međureprezentacije. Svaki od dodanih primitiva odgovara jednoj od hardverski podržanih operacija konvolucije s filtrima različitih dimenzija.

Jedan od inicijalnih ciljeva ove disertacije bio je podići razinu apstrakcije za kompleksne heterogene sustave. Jedan od razloga takvog pristupa jest i taj što takve sustave često koriste znanstvenici u pojedinim domenama bez iskustva u području programiranja. Dodatno, kompleksni heterogeni sustavi za puno iskorištavanje njihovih mogućnosti često zahtijevaju poznavanje arhitekturalnih detalja na niskoj razini, te na taj način čine cjelokupni proces pro-

gramiranja takvog sustava inherentno teškim. Podizanje razine apstrakcije *de facto* zahtjeva prebacivanje odgovornosti za poznavanje tih detalja na prevoditelj. Uzevši sve u obzir, a u svrhu ostvarenja cilja disertacije, implementiran je mehanizam detekcije odgovarajućih uzoraka koji se mogu izvesti u hardverski implementiranim specijaliziranim ubrzivačima. Konkretno, za platformu GAP8, u programskom jeziku ELEVATE implementirano je pravilo koje prepoznaje slijed uzoraka operacije konvolucije te ga prevodi u jedan od prethodno opisanih odgovarajućih konvolucijskih primitiva u programskom jeziku RISE. Na taj način se omogućuje da se ispravno izražena operacija konvolucije izvrši u hardverskom ubrzivaču operacije konvolucije, a bez eksplicitnog navođenja poziva te bez potrebe za poznavanjem arhitekturalnih detalja ciljne platforme. Konkretni primitiv u koji se izraz prevodi ovisi o veličini susjedstva koji je zadan kao parametar primitivu *slide2D*.

Na niskoj razini, kao dio potporne infrastrukture za generiranje kôda, implementirana je i knjižnica za izvedbenu okolinu (*eng. runtime library*). Ta knjižnica izlaže sučelje koje je unificirano za ciljne platforme koje podržavaju koncept domaćina i uređaja, a cilj jest smanjiti količinu repetitivnog kôda koju generator kôda unutar RISE okvira mora generirati. Generator kôda generirat će pozive izložene ovom knjižnicom, a pojedine platforme implementiraju pozive na niskoj razini, uvažavajući vlastite specifičnosti. Knjižnica je izvorno nastala za OpenCL platforme, a na odgovarajući način je proširena te implementirana za platformu GAP8. Glavni koncepti koje knjižnica uvodi su kontekst, jezgra (*eng. kernel*) te *buffer*. Kontekst enkapsulira sve potrebne informacije za izvođenje akceleratorske funkcije na klasteru, dok jezgra (*kernel*) enkapsulira samu akceleratorsku funkciju koja će se izvesti na klasteru. *Buffer* predstavlja dio memorije u kojem se nalaze podaci nad kojima se izvršavaju operacije. Uvođenjem koncepta *buffera* anticipira se mehanizam transfera podataka s domaćina na uređaj i obrnuto, ali se ti transferi u ovom trenutku ne događaju, što je indicirano implementacijom u datoteci *nosync.c.*

Implementacija modela zaokružena je komponentom izvođača koja omogućava izvođenje programa u prirodnom okruženju okvira RISE, ali na ciljnoj hardverskoj platformi ili unutar simulatora. Izvođač enkapsulira generiranje kôda, prevođenje na niskoj razini nativnim prevoditeljem za ciljnu platformu, te izvršavanje na ciljnoj platformi. Kao parametre moguće je specificirati ciljnu platformu u vidu testne pločice ili simulatora, operacijski sustav, te kanal za komunikaciju s programerom. S obzirom na to da se na niskoj razini programi za GAP8 prevode korištenjem programa make, izvođač popunjava varijable u predefiniranoj datoteci Makefile.

## 6. Evaluacija modela

Kao dodatni doprinos, prethodno izloženi model ekstenzivno je evaluiran s obzirom na performanse, energetsku učinkovitost te programirljivost. Evaluacija je provedena na način uspoređivanja prethodno navedenih parametara za ručno optimiran kôd te kôd generiran proširenim programskim okvirom RISE. Metodologija mjerenja uvijek je bila identična, a sastojala se od pet uzastopnih mjerenja, od kojih je prvo odbačeno kako bi se eliminirali potencijalni negativni

efekti utitravanja ispitne okoline. Performansa i energetska učinkovitost mjerila se samo za izračun od interesa, dok podizanje sustava, učitavanje podataka te ispis rezultata nisu bile uzimane u obzir. U konačnici, dobiveni rezultati prikazani su kao prosjek i standardna devijacija uzorka. Za provođenje mjerenja pratile su se službene upute proizvođača ispitne okoline.

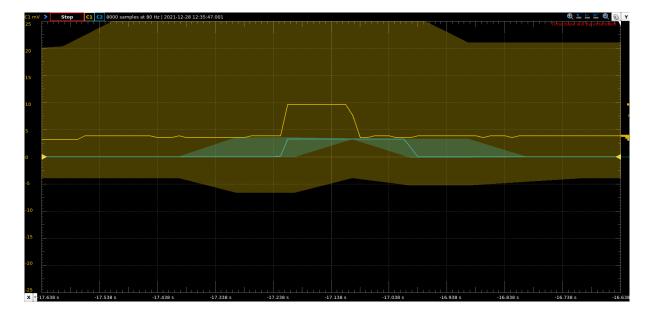

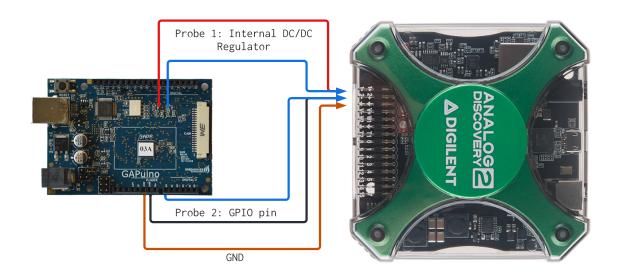

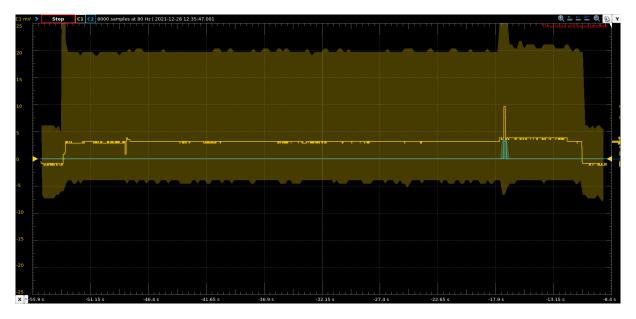

Mjerenje performanse mjerilo se dvama parametrima: praćenjem broja aktivnih ciklusa te stvarno proteklog vremena potrebnog za izvršavanje s obzirom na "zidni sat". Za oba parametra korišten je GAP8 API, a na odgovarajuća mjesta u kôdu ubačeni su odsječci koji pokreću mjerenje prije pokretanja ispitnog izračuna, te zaustavljaju mjerenje nakon izračuna. Energetska učinkovitost mjerena je kroz potrošnju energije za vrijeme trajanja izračuna od interesa. Prva diferencijalna sonda osciloskopa spojena je na izvode internog DC/DC regulatora GAP8 čipa. Između izvoda smješten je otpornik vrijednosti 1 Ohm čime je izravno omogućeno mjerenje struje kroz otpor te posljedično snage u diskretnim trenutcima izvođenja. Uzorkovanjem sonde, mjerene su vrijednosti napona te je izračunata snaga, a numeričkom integracijom snage s obzirom na vrijeme izvođenja, izračunata je potrošnja energije. Za verifikaciju, energija je izračunata i korištenjem prosječne snage za vrijeme izvođenja izračuna od interesa. Za označavanje izračuna od interesa korištena je druga diferencijalna sonda osciloskopa koja je bila spojena na GPIO priključnice sustava. Ta je priključnica na odgovarajućim mjestima u programskom kôdu bila postavljana u logičku jedinicu te spuštana u logičku nulu. Označavanje izračuna od interesa pokazalo se potrebnim iz razloga fluktuiranja napona na izvodima internog DC/DC regulatora čime je onemogućeno da se vršne vrijednosti tog napona smatraju početkom i krajem izračuna od interesa. Osciloskop je obje sonde uzorkovao frekvencijom od 1 kHz.

Za ispitne scenarije uzete su aplikacije iz stvarne primjene. Prvi ispitni scenarij je množenje matrica, a korištene su matrice dimenzija  $250 \times 250$  elemenata. Drugi ispitni scenarij je Sobelov filter kojime se u slikama naglašavaju oštriji kontrastni prijelazi. Iako se ovaj filter svodi na operaciju konvolucije s dva različita filtra te geometrijsku sredinu kao konačan rezultat, prilikom izračuna radi nestabilnosti nije korišten hardverski ubrzivač operacije konvolucije. Testni podatak je monokromatska slika dimenzija  $320 \times 240$  piksela. Treći i posljednji ispitni scenarij je klasteriranje k-sredinama, algoritam koji ima izravne primjene u strojnom učenju, a koristi se za klasteriranje m točaka s n dimenzija u k klastera. Za testiranje korišten je skup podataka o 250 točaka s dvije dimenzije u tri klastera, a postupak je provođen u 1000 iteracija algoritma. Barnes-Hut simulator n tijela izbačen je kao ispitni scenarij radi poteškoća u prilagodbi ručno optimiranog kôda za ispitnu platformu. Jedan ispitni scenarij korišten je u svrhu verifikacije, te za njega nisu provedena mjerenja. Taj scenarij jest verifikacija prevođenja operacije konvolucije izražene u programskom jeziku RISE za izvođenje na hardverskom ubrzivaču operacije konvolucije. Za ovaj slučaj prikazana je primjena jednostavne optimizacijske strategije koja izraženu konvoluciju prilagođava za izvođenje na hardverskom ubrzivaču.

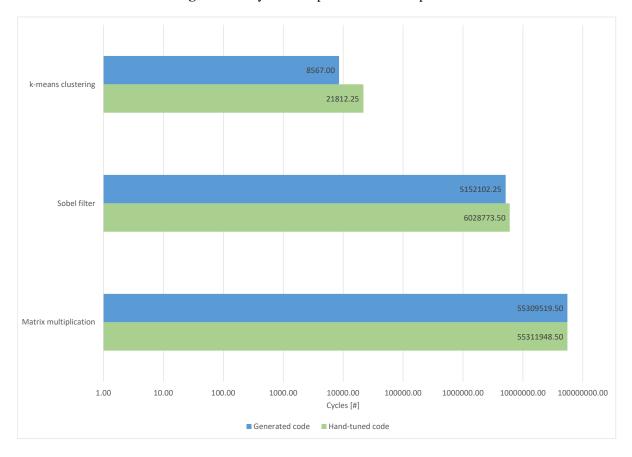

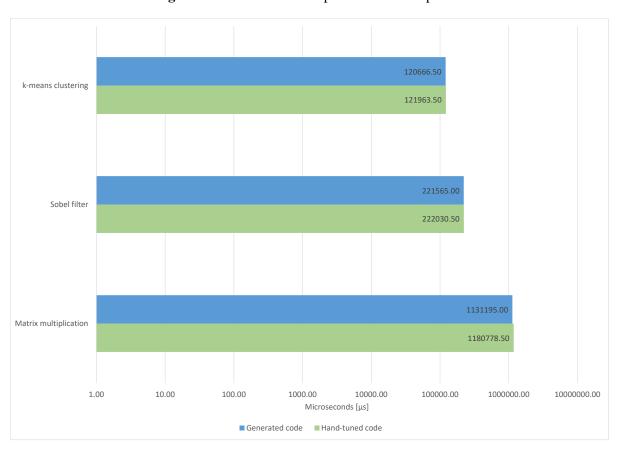

Postignuti rezultati za performanse su zadovoljavajući. S obzirom na mjerenje protek-

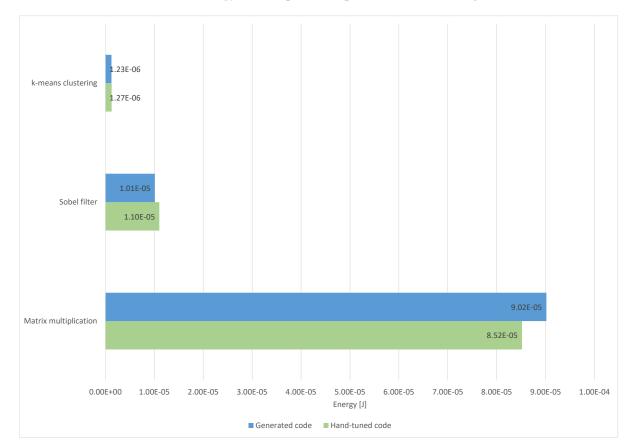

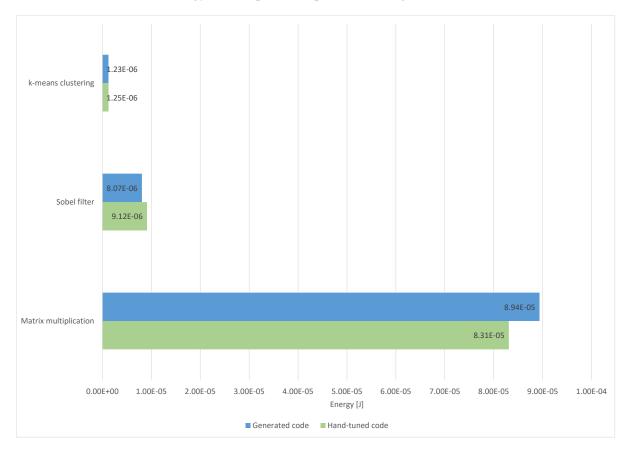

log vremena ispitnog izračuna, generirani kôd postiže rezultate koji su marginalno bolji od ručno optimiranog kôda. Kada se promatraju rezultati s obzirom na broj aktivnih ciklusa, rezultati su također marginalno bolji od ručno optimiranog kôda, s izuzetkom klasteriranja k-sredinama gdje je performansa generiranog kôda značajnije veća od ručno optimiranog kôda. Potonji slučaj može se zanemariti jer je očekivano da rezultat ostvaren brojem aktivnih ciklusa odražava rezultat ostvaren proteklim vremenom. Moguće odstupanje, iako pozitivno za doprinos disertacije, vjerojatno je uzrokovano internim brojačima performansi unutar GAP8 API, a koji u ovom trenutku radi nedostatka resursa nije podrobnije analiziran. Evaluacija energetske učinkovitosti također je dala zadovoljavajuće rezultate. Za sva tri ispitna scenarija, te za obje metode mjerenja, rezultati generiranog kôda sumjerljivi su ručno optimiranom kôdu. Scenariji klasteriranja k-sredinama i Sobelovog filtra marginalno su bolji za generirani kôd, dok je rezultat množenja matrica marginalno lošiji, ali svejedno sumjerljiv ručno optimiranom kôdu.

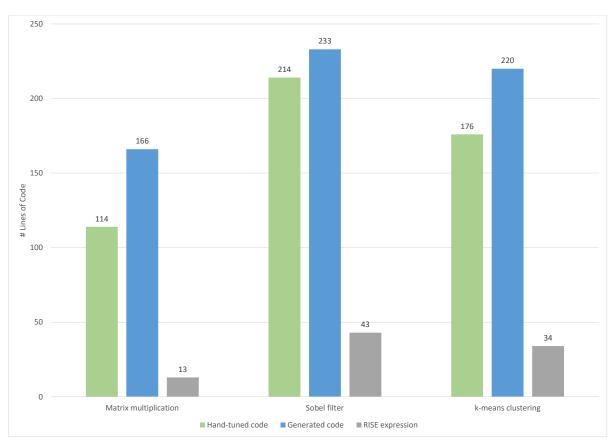

Mjerenje programirljivosti izvršeno je implicitno, a s obzirom na to da su se metrike za ocjenu programirljivosti pojedinih programskih modela pokazale nepouzdanima ili subjektivnima, za ovu svrhu prebrojane su linije programskog kôda za ručno optimirani kôd, generirani kôd, te kôd u programskom jeziku RISE. Za sve slučajeve kôd u programskom jeziku RISE značajno je kraći od ručno optimiranog kôda. Generirani kôd je duži od ručno optimiranog kôda, ali se taj slučaj može zanemariti s obzirom na to da se generiranje kôda može percipirati kao jedan od koraka u prevoditeljskom lancu. Kôd u programskom jeziku RISE je kraći, čistiji i koncizniji te se može tvrditi da je uz postignute sumjerljive rezultate za postignute performanse i energetsku učinkovitost prikladan za korištenje u heterogenim sustavima.

## 7. Zaključak

Vršne performanse superračunala današnjice mjerene jedinicom FLOPS, trenutno su reda veličine *petaFLOPS* (10<sup>15</sup>). Radi napretka čovječanstva, a posljedično i znanosti, anticipira se skorija potreba za ulaskom tzv. *exascale* domenu u kojoj će vršne performanse biti u razini *exaFLOPS* (10<sup>18</sup>). Za dostizanje *exascale* domene, ključni faktori su efikasno iskorištavanje paralelizma te heterogenost. Jedan od problema s kojima se programeri i znanstvenici susreću u radu s takvim, visoko paralelnim i heterogenim, sustavima jest programiranje. Efikasno iskorištavanje dostupnih resursa često zahtjeva poznavanje arhitekturalnih detalja niske razine. Cilj ove disertacije bio je podići razinu apstrakcije, te izložiti jezik visoke razine za efikasnije programiranje kompleksnih heterogenih sustava. Taj cilj je i dostignut proširenjima programskog jezika RISE te pripadajućeg okvira. Usporedba performansi te energetske učinkovitosti postignutih generiranim kôdom u odnosu na ručno optimirani kôd pokazuje da je moguće barem zadržati, a često i postići bolje performanse i energetsku učinkovitost.

Buduće optimizacije na praktičnom dijelu doktorskog rada moguće su u više pravaca. Prvi mogući pravac jest optimizacija i bolje iskorištavanje memorijskog podsustava. Trenutno se svi podaci nad kojima se vrši obrada pohranjuju u memoriji koja je dostupna cijelom sustavu,

ali je ujedno i najsporija. Paralelizacijom obrade i transfera podataka u bržu memoriju rezerviranu isključivo za klaster, nedvojbeno bi se postigle više razine performansi i energetske učinkovitosti, uz zadržavanje iste razine programirljivosti. Optimizacijska strategija za detekciju uzoraka koji predstavljaju operaciju konvolucije je prespecifična te ne anticipira mogućnost da se konvolucija izrazi na moguće drugačiji način, te je strategiju u tom kontekstu moguće dodatno optimirati. S druge strane, strategiju se može generalizirati i na način da se implementira mogućnost operacija konvolucije za signale i filtre različitih dimenzionalnosti. Zadnji pravac u kojem je moguće dati doprinos jest dodatno pojednostavljenje modela. Trenutni model predstavlja napredak u odnosu na nativan programski model za ciljnu platformu, ponajprije radi izlaganja konciznijeg sučelja, ali i sakrivanja arhitekturalnih detalja niske razine. Ipak, funkcijska programska paradigma, još uvijek je relativno nepoznata te se model može prilagoditi dodatno kako bi se programiranje kompleksnih heterogenih sustava dodatno pojednostavnilo.

**Ključne riječi**: domenski specifični jezici, heterogeni sustavi, paralelno procesiranje, višejezgreni sustavi, RISC-V

## **Contents**

| 1.        | Intro    | duction                                                                                      | 1                                                                                                                                                                                                                                                                                                | 1   |

|-----------|----------|----------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|           | 1.1.     | Resear                                                                                       | ch goals                                                                                                                                                                                                                                                                                         |     |

|           | 1.2.     | Thesis                                                                                       | outline                                                                                                                                                                                                                                                                                          |     |

| 2.        | The      | oretical                                                                                     | Background                                                                                                                                                                                                                                                                                       | 8   |

|           |          |                                                                                              | l motivation                                                                                                                                                                                                                                                                                     |     |

|           | 2.2.     | Paralle                                                                                      | lism                                                                                                                                                                                                                                                                                             |     |

|           |          | 2.2.1.                                                                                       | Levels of parallelism                                                                                                                                                                                                                                                                            |     |

|           |          |                                                                                              | Programming models                                                                                                                                                                                                                                                                               |     |

|           | 2.3.     |                                                                                              | geneous systems                                                                                                                                                                                                                                                                                  |     |

|           |          | 2.3.1.                                                                                       | Heterogeneity as a concept                                                                                                                                                                                                                                                                       |     |

|           |          | 2.3.2.                                                                                       | Accelerators                                                                                                                                                                                                                                                                                     |     |

|           |          | 2.3.3.                                                                                       | GPGPUs                                                                                                                                                                                                                                                                                           |     |

|           |          | 2.3.4.                                                                                       | Other                                                                                                                                                                                                                                                                                            |     |

| •         | <b>C</b> | 1 C                                                                                          | agents                                                                                                                                                                                                                                                                                           | 1 ( |

| 3.        | Gene     | erai Coi                                                                                     | icepis                                                                                                                                                                                                                                                                                           | い   |

| <b>5.</b> |          |                                                                                              | ncepts                                                                                                                                                                                                                                                                                           | 1 > |

| 3.        |          |                                                                                              | n-specific languages                                                                                                                                                                                                                                                                             | 1 > |

| <b>3.</b> |          | Domai 3.1.1.                                                                                 | n-specific languages                                                                                                                                                                                                                                                                             | 15  |

| 3.        | 3.1.     | Domai 3.1.1. 3.1.2.                                                                          | General                                                                                                                                                                                                                                                                                          |     |

| 3.        | 3.1.     | Domai 3.1.1. 3.1.2. RISC-Y                                                                   | General                                                                                                                                                                                                                                                                                          | 13  |

| 3.        | 3.1.     | Domai 3.1.1. 3.1.2. RISC-3.2.1.                                                              | n-specific languages       .19         General       .19         Overview of the field       .20         V       .25         General       .25                                                                                                                                                   | 13  |

| 3.        | 3.1.     | Domai 3.1.1. 3.1.2. RISC-7 3.2.1. 3.2.2.                                                     | n-specific languages       .19         General       .19         Overview of the field       .20         V       .25         General       .25         Extensions       .25                                                                                                                      |     |

| 3.        | 3.1.     | Domai 3.1.1. 3.1.2. RISC-3.2.1. 3.2.2. 3.2.3.                                                | n-specific languages       .19         General       .19         Overview of the field       .20         V       .25         General       .25         Extensions       .25         Notable projects       .28                                                                                   |     |

| 3.        | 3.1.     | Domai<br>3.1.1.<br>3.1.2.<br>RISC-<br>3.2.1.<br>3.2.2.<br>3.2.3.<br>PULP                     | n-specific languages       .19         General       .19         Overview of the field       .20         V       .25         General       .25         Extensions       .25         Notable projects       .28          .29                                                                      |     |

| 3.        | 3.1.     | Domai<br>3.1.1.<br>3.1.2.<br>RISC-Y<br>3.2.1.<br>3.2.2.<br>3.2.3.<br>PULP<br>3.3.1.          | n-specific languages       .19         General       .19         Overview of the field       .20         V       .25         General       .25         Extensions       .25         Notable projects       .28          .29         Processors       .30                                         |     |

| 3.        | 3.1.     | Domai<br>3.1.1.<br>3.1.2.<br>RISC-<br>3.2.1.<br>3.2.2.<br>3.2.3.<br>PULP<br>3.3.1.<br>3.3.2. | n-specific languages       .19         General       .19         Overview of the field       .20         V       .25         General       .25         Extensions       .25         Notable projects       .28          .29         Processors       .30         Single core platforms       .30 |     |

| 3.        | 3.1.     | Domai<br>3.1.1.<br>3.1.2.<br>RISC-Y<br>3.2.1.<br>3.2.2.<br>3.2.3.<br>PULP<br>3.3.1.          | n-specific languages       .19         General       .19         Overview of the field       .20         V       .25         General       .25         Extensions       .25         Notable projects       .28          .29         Processors       .30                                         |     |

|           | 3.4. | GAP8    |                                      | .33  |

|-----------|------|---------|--------------------------------------|------|

|           |      | 3.4.1.  | Architecture of the platform         | .34  |

|           |      | 3.4.2.  | API                                  | .35  |

| 4.        | DICI | F Stock |                                      | 13   |

| <b>4.</b> |      |         |                                      |      |

|           |      |         | al concepts                          |      |

|           | 4.2. |         | & Shine                              |      |

|           |      |         | General                              |      |

|           | 4.2  | 4.2.2.  | r                                    |      |

|           |      |         | ATE                                  |      |

|           | 4.4. | Notable | le research                          | .53  |

| 5.        | Mod  | el Impl | lementation                          | . 54 |

|           | 5.1. | Genera  | al                                   | .54  |

|           | 5.2. | GAP8    | Module                               | .55  |

|           | 5.3. | Code g  | generation                           | .56  |

|           |      | 5.3.1.  | Accelerator code generation          | .56  |

|           |      | 5.3.2.  | Host side                            | .58  |

|           | 5.4. | Expres  | ssion running mechanism              | .61  |

|           |      | 5.4.1.  | Host and accelerator code separation | .62  |

|           | 5.5. | Hardw   | rare convolution engine support      | .63  |

|           |      | 5.5.1.  | Optimization strategy                | .65  |

|           | 5.6. | Runtin  | ne environment                       | .67  |

|           | 5.7. | Execut  | tor                                  | .71  |

|           |      |         |                                      |      |

| 6.        |      |         | uation                               |      |

|           | 6.1. |         | dology                               |      |

|           |      | 6.1.1.  | Performance measuring                |      |

|           |      | 6.1.2.  | Measuring energy consumption         |      |

|           | 6.2. |         | marks                                |      |

|           |      | 6.2.1.  | Matrix multiplication                |      |

|           |      | 6.2.2.  | Sobel filter                         | .81  |

|           |      | 6.2.3.  | k-means clustering                   | .84  |

|           |      | 6.2.4.  | Convolution                          | .86  |

|           | 6.3. | Evalua  | ation                                | .89  |

|           |      | 6.3.1.  | Performance evaluation               | .89  |

|           |      | 6.3.2.  | Energy efficiency evaluation         | .92  |

|           |      | 6.3.3.  | Programability evaluation            | .95  |

| 7.  | <b>Conclusion</b>           |

|-----|-----------------------------|

| A.  | Hand-tuned code             |

| B.  | <b>Generated code</b>       |

|     | B.1. Sobel filter benchmark |

|     | B.2. HWCE utilization       |

| Bil | bliography                  |

| Bio | ography                     |

| Živ | votopis                     |

## **Chapter 1**

## Introduction

Nowadays as we observe stable and constant growth in science and the general advancement of humanity, the increased need for computational resources is observed as well. Raw computing performance measured in FLOPS (Floating Point Operations Per Second), a de facto standard in measuring computational performance, especially in the high-performance computing domain, according to the Top500 list [1], is currently in Peta (10<sup>15</sup>) order of magnitude. Although currently achieved peak performance levels satisfy today's needs for computing power, the need to enter the ExaFLOPS (10<sup>18</sup>) domain with affordable energy consumption is anticipated and is currently one of the goals for computer engineers and scientists. In his opening keynote at the international high-performance computing conference SC20, Bjorn Stevens, a professor at the Max Planck Institute for Meteorology in Hamburg, Germany said that a real need for exascale computing power exists. As an example, he pointed out the massive data sets created by climate science, while stressing out that the computing power has to be accessible to a wide range of people [2].

The importance of achieving the Exascale domain is confirmed by the existence of the research projects in different parts of the World, e. g. "Exascale Computing Project" in USA [3], Japan [4] with allegations that China has already reached exascale on two separate systems [5]. Japan's Fugoku supercomputer built on ARM processor architecture and Tofu interconnect D already reached exascale domain in single or further-reduced precision [1]. European Union also heavily invests in High-performance computing, with aims towards Exascale as well [6], with a couple of notable projects like EuroHPC initiative [7], European Open Science Cloud (EOSC) [8], and ExaNode project [9].

The latter is heavily influenced by the current geopolitical perspective, due to the fact that most of the processing cores manufacturers are non-European. Intel, AMD, and NVIDIA are located in the USA, while ARM resides in the UK which can't be considered to be politically tied to the European Union any longer. Furthermore, NVIDIA is in process of acquiring ARM which will even more derogate the European intelligence on processing cores design.

Everything mentioned renders Europe and the European Union vulnerable, which is additionally amplified by the rise of tensions on the current geopolitical map of the world. In light of that, it is necessary to mention Europe Processor Initiative (EPI) [10] which aims to deliver a new family of low-power European processors for extreme-scale computing, high-performance Big-Data and a range of emerging applications [11], together with the processing cores design know-how, guaranteeing its processing sovereignty. EPI is a project currently implemented under the special sponsorship of the European Commission which further stresses the importance of the project in the context of European computing sovereignty, both in High-Performance and general computing domains.

The so-called Exascale domain opens up many challenges, mainly in the areas of computer architecture, heterogeneity, and energy efficiency, and it is exactly the heterogeneity that is one of the key development points with respect to reaching the Exascale domain [12]. Heterogeneity, in the most general case, purports the usage of multiple processing cores with different purposes and architectures inside one relatively isolated computational node.

Usually, considering a computational node, besides a general-purpose processor, heterogeneity implies the existence of the general-purpose graphics processing unit (GPGPU) or accelerator for specific applications or tasks. The concept of heterogeneity gained popularity exactly when graphic processing units' manufacturers exposed their cores to general computing by the appropriate APIs, CUDA [13] for NVIDIA chips and OpenCL [14] for AMD chips. General-purpose graphic processing units introduced a significant increase in performance in the intensive data-parallel applications. In these domains, they are significantly more energy-efficient than general-purpose processors. Also, they can be simply horizontally scaled by switching to newer models, which represents a perk being reasoned by the fact that Moore's law is still applicable to them. A major advantage is a considerably simpler programming model for the average programmer, exposed through the aforementioned CUDA and OpenCL, with the addition of OpenMP, when compared to programming and synthesizing custom accelerators.

The other important type of processing unit in the context of heterogeneity are customized accelerators which are implemented as locked, custom components, or customizable programmable logic implemented in FPGA chips. Such accelerators achieve higher performance and energy efficiency compared to conventional processing engines and graphic processing units, but that comes with a price: complicated programming model at the level of hardware design, lack of scalability, lack of portability, and usability only in application domain they were designed for. Tools that ease the implementation of customized accelerators exist, i.e. Chisel [15] or Highlevel synthesis techniques, but they haven't, due to multiple reasons, been caught on in general usage.

The combination of types of processing units in a heterogeneous environment is generally context-dependent. In embedded devices where energy efficiency and spatial conservativeness

prevail, heterogeneous devices usually combine a general-purpose processor with an application accelerator. On the other hand, High-performance computing usage scenarios utilize general-purpose graphic processing units and application-specific accelerators as well.

Intel's acquisition of Altera (today known under the name Intel FPGA), one of the two major FPGA suppliers, clearly indicates that future computing platforms will add more heterogeneity in the form of reconfigurable fabric, while in the high-performance computing domain, several initiatives already employ heterogeneous systems with CPUs, GPGPUs and large arrays of FPGA fabric, such as Amazon's EC2 F1 [16] and Microsoft's Catapult [17], with the latter being now deployed in nearly every new server across the more than a million machines that the Microsoft's hyperscale cloud consists of [18]. The trend is also visible in the Top500 list where nearly 30% of the systems use the accelerator or co-processor technology [19]. The main reason accelerators are not (yet) more widely employed in high-performance systems is the difficulty encountered in writing software that exploits accelerators' capabilities efficiently [20], a problem which persisted up until today.

Given the multiple advantages and drawbacks of both the general-purpose graphic processing units and customized acceleration engines, there exists a large gap for customizable accelerators which would combine advantages while minimizing flaws of both approaches. Such accelerators are flexible enough to avoid applicability-lock on just one type of application, and in every application domain they would achieve performance and energy efficiency commensurate with completely customized accelerators. Packed with the programming interface exposed through a domain-specific language, a complicated programming model could be avoided as well. In addition, their adjustability enables co-design and high-level architectural explorations for performance or energy efficiency optimization of the system running target application from one of the selected disruptive domains, such as machine learning, crypto processing, or multimedia processing.

When discussing parallelism and heterogeneity in education, most of the curricula that are being thought at the universities worldwide consist of teaching students sequential programming in the introductory courses. The problem arises because sequential programming heavily influences the sequential way of thinking. As stated before, virtually all of the computers that are surrounding us are multicores, and while we are surrounded by multicores, we still tend to teach students sequential programming and thinking [21]. Arguably, teaching the parallel way of thinking since the inception of one's education in computer science could be better than teaching imperative and sequential paradigms to only then teach how to parallelize algorithms or code in general. Furthermore, the latest guidelines published jointly by the ACM and the IEEE in 2013. recommended integration of the parallelism throughout the curriculum [22]. Parallel programming, together with the exploitation of heterogeneous hardware is inherently hard, starting from exploiting general-purpose graphic processing units to specific accelerators.

To ease programming and increase the exploitation of computational power of such systems we have to develop new methods and models.

Finally, following everything discussed so far, this thesis aims to cope with the emerging heterogeneity and the inherent need to increase level of parallelism, together with the need of easing parallel programming models by providing a novel programming model. The provided model is formed as a domain-specific language which with the provided compiler infrastructure compiles to the native model for the target in question.

## 1.1 Research goals

The main goal of this research is to provide an adequate programming model for complex heterogeneous systems with scalable and customizable acceleration engines based on the computational patterns that constitute the most compute-intensive kernels in selected application domains, as well as support computations that heavily rely on integer or fixed-point bit-manipulation with extreme producer-consumer parallelism. From the theoretical point of view, the research will provide a comprehensive review of the programming models used for heterogeneous systems with an emphasis on compilers and infrastructure which implicitly encourages and supports parallelization. The practical implication will be a programming language for heterogeneous systems with customizable accelerators. One of the outcomes is to evaluate the complete solution, namely the implemented programming model, to test it and compare it with the hand-tuned code both in domains of performance and energy efficiency.

The hypotheses of the research are:

- 1.It is possible to express complex problems stemming from various domains in a domainspecific language which can target heterogeneous systems

- 2.Performance of the code generated by the provided infrastructure is better or at least on par with the hand-tuned code

- 3.Energy efficiency of the hardware which executes code generated by the provided infrastructure is better or at least on par with the hand-tuned code

- 4.Programmability of the complex heterogeneous systems is higher when using the proposed programming model compared to the conventional programming model for the same platform

The starting point of this research is the efficient programming abstraction for programming complex heterogeneous systems with customizable accelerators. Given the context, the ground case for the research is a domain-specific language layer that will be modeled or adjusted to conform to the needs of such systems. The proposed language will be implemented together with the rest of the components defined by the expected scientific contribution.

Regarding the planned testing equipment, an adequate system has been detected in GAP8

[23] chip by GreenWaves Technologies. GAP8 is a heterogeneous system on chip which is consisted of a general-purpose processing core based on RISC-V ISA named Fabric Controller and an accelerator featuring 8 cores and a custom hardware convolution engine. Both fabric controller and cores available in the cluster implement the same RISC-V instruction set, that is RV32IMC. GAP8 stems from the PULP project [24], more specifically from *Mia Wallace* [25] and Open Heterogeneous Research Platform - HERO [26]. Concepts presented in both platforms can be found in GAP8. One such example is the bigPULP accelerator available in HERO being exactly the cluster in the GAP8 platform, with differences in the general-purpose processor which is ARM in HERO, and RISC-V based core in GAP8.

This thesis aimed to fulfill the expected scientific contribution proposed at the public thesis topic defense which is constituted through 2 parts:

- 1.Programming model for heterogeneous systems with customizable accelerators based on a domain-specific language

- 2.Algorithms for accelerator customization based on program features for performance and energy efficiency optimization

The first part of the expected scientific contribution is fulfilled through the extension of the RISE language and integration of the target platform in the Shine compiler infrastructure. Support for the target platform was carried out by the addition of the primitives necessary to support target-specific operations, together with primitives necessary to run expressions written in RISE on the target platform.

The development of the second part of the expected scientific contribution was heavily influenced by the eventual inexistence of the desired type of customizable accelerators that were anticipated by the project and the research described through this thesis. The idea proposed through public thesis topic defense anticipated the future existence of the accelerators that would expose tunable parameters, such as integer or floating-point precision, making them usable in more than one application domain. However, the concept of such accelerators, though promising, never ended with a usable prototype, let alone with a concrete and usable implementation. Some of the parameters can be set up, like clock frequency of the fabric controller and cluster, together with the voltage of the chip, but tuning those parameters can't be considered customizing the accelerator itself. However, given the final type of customizable accelerators that were used in this thesis, optimization techniques available in the Shine compiler were utilized. Furthermore, as an addition to the scientific contribution, support for the customized piece of hardware embodied through available Hardware Convolution Engine was added, together with optimization strategy which transforms one of the series of patterns that express convolution in RISE. The latter serves as a showcase of supporting customized hardware through pattern rewriting when a series of patterns that constitute a computation supported by the aforementioned customized hardware is detected. Also, additional optimizations are possible in the future, regarding the detection of additional series of patterns that could constitute convolution operation, and thus be supported by the hardware convolution engine. Finally, this thesis also provides a number of benchmarks and example applications of the proposed model, which were not initially proposed by the expected scientific contribution.

## 1.2 Thesis outline

Besides the introduction which introduces a reader to the thesis topic, explains scientific contribution and hypotheses, this thesis is divided into seven chapters and two appendices which are organized as follows:

## Chapter 2 Theoretical Background

This chapter additionally widens the motivation for research in this field by providing the necessary temporal context regarding the current state of the computing systems. Additionally, some fundamental concepts regarding heterogeneity, parallelism, and techniques to efficiently exploit parallelism on multiple levels are provided.

## **Chapter 3** General Concepts

This chapter covers a wide aspect of topics needed for the complete understanding of the thesis. Topics that are covered include domain-specific languages, RISC-V, PULP, and GAP8, with some of them packed together with the state-of-the-art in the respective topic.

## **Chapter 4** RISE Stack

Chapter **RISE Stack** gives a brief introduction to the data-parallel pattern-based RISE programming language and to ELEVATE, a language used to express optimization strategies. A brief overview of the programming framework used to utilize these two languages is provided, together with a description of the Shine compiler used to compile programs from expressions written in RISE to low-level code.

## **Chapter 5** Model Implementation

In **Model Implementation** chapter, every aspect of the extensions to the RISE framework is described, including code generation, module generation, code separation, expression transformation, and code execution.

## **Chapter 6** Model Evaluation

Chapter **Model Evaluation** evaluates the proposed solution on different benchmarks, including a benchmark that verifies code correctness for utilization of the HWCE, in terms of performance, energy efficiency, and programmability. The evaluation methodology is described, and the results are discussed.

## **Chapter 7** Conclusion

Finally, chapter **Conclusion** concludes this thesis with an overview of everything provided in it and some perspective proposals for future work.

## Appendix A

This appendix provides an example of hand-tuned code, which was used in performance and energy efficiency comparisons. The hand-tuned code for the Sobel filter benchmark is provided.

**Appendix B** This appendix provides a couple of examples of the generated code used in comparisons. For consistency, generated code for the Sobel filter benchmark is provided. Additionally, an example of the generated code that utilizes HWCE is provided.

## **Chapter 2**

## **Theoretical Background**

This chapter provides the necessary background, in terms of concepts and literature overview necessary for the understanding of the thesis outcomes. The main concepts that are introduced are parallelism and heterogeneity with their description, techniques, and a brief overview of the concept's field.

## 2.1 General motivation

Moore's law, a de facto standard for approximation of transistor on integrated circuits stated that the aforementioned number doubles approximately every two years. The author of the law himself not so recently stated that he sees the "Law dying here in the next decade or so" [27, 28]. A similar conclusion came from the acting CEO of NVIDIA at the prestigious CES 2019 conference [29]. Although part of the chipmakers still does not perceive the law dead, it is indeed a fact that the on-chip transistor growth slowed down, mostly because the technology reached its physical limits.

Furthermore, the perceived exponential growth of the effective computing power faded away by hitting three types of "wall" [30], namely [31]:

- **Power wall** As a result of the significant increase in frequency, the ability to dissipate heat has reached the physical limit. Furthermore, the ratio between energy consumption and increase in performance is not linear.

- Instruction-Level parallelism (ILP) wall ILP causes a super-linear increase in complexity and power consumption of the processing unit without linear speed up in the application performance. To put it simply, one has to add complex pipelines that are not mirrored in an equal performance increase

- Memory wall The mismatch between memory speed and computation speed

From the latter follows that augmented with the fact that Moore's law definitely sees its end at some point in the relatively near future, new hardware has to be designed and developed in

multicore or multichip fashion to deliver expected higher performance. Consequently, programs need to be developed in such a manner to exploit underlying multicore systems. Drive for the ever-lasting higher performance has to imply parallelism.